Using Vivado 2018.3 .

I2C EEPROM operation

I have xx24C64 on my board:

- 8 KB (64 Kb) space

- Address range 0~0x1FFF

- Device address

7’b101_0011,0x53(on my board, A2=0, A1=A0=1)

Datasheet: CAT24C64 - 64 Kb I2C CMOS Serial EEPROM (onsemi.com)

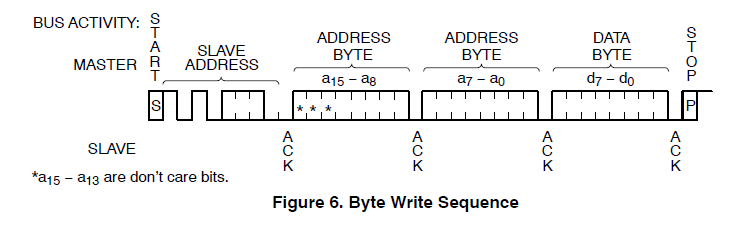

Byte Write

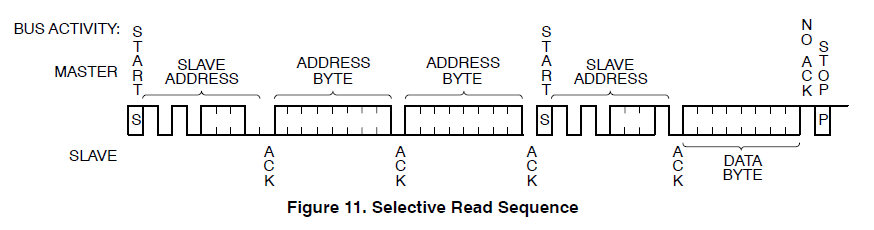

Selective Read

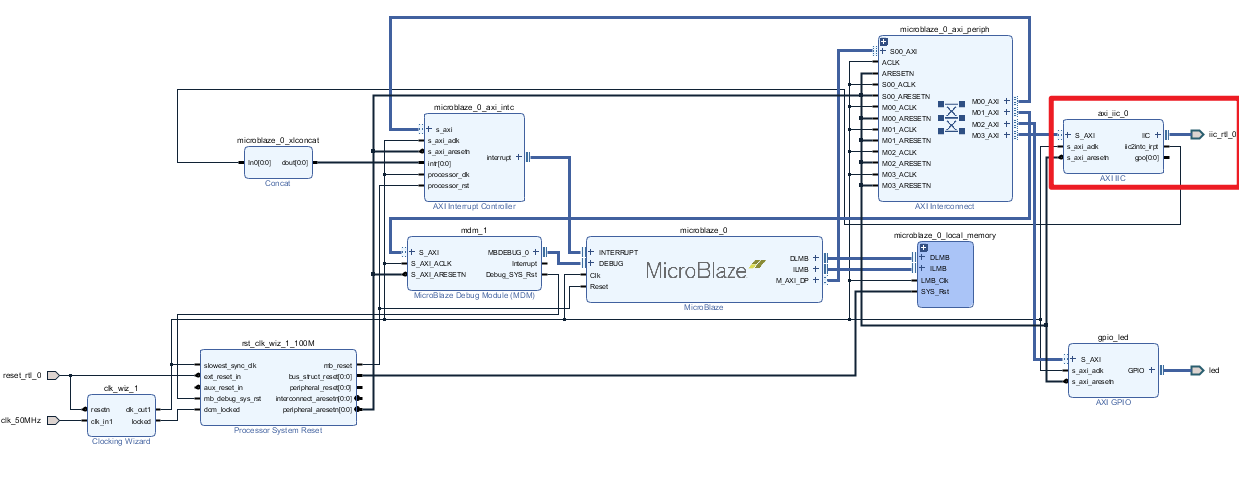

Vivado Block Design

Except for the AXI_IIC IP, other settings are the same as the block design in Microblaze2.1 JTAG-UART | QY’s Notes.

I2C Polled-mode

From xiic documentation, iic: Main Page:

This driver does not provide a polled mode of operation primarily because polled mode which is non-blocking is difficult with the amount of interaction with the hardware that is necessary.

So, at first, I thought interrupt was necessary… Until I find this example: xiic_low_level_eeprom_example.c

Since I only wanted to configure an I2C slave device, polled-mode with blocking is fine.

Basically, I just need XIic_Recv() and XIic_Send().

And the job was done. I guess I won’t be using microblaze in a while…

Resource

- 24C64 Datasheet: CAT24C64 - 64 Kb I2C CMOS Serial EEPROM (onsemi.com)

- Xilinx Github : iic: xiic_l.c File Reference

- AXI_IIC读写操作_axi iic_丁点的沙砾的博客-CSDN博客

- IIC Protocol and Programming Sequence (xilinx.com)

- Xilinx FPGA Microblaze AXI_IIC使用方法及心得_axi iic_NjustMEMS_ZJ的博客-CSDN博客

Sample Code

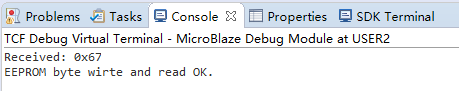

Run result: write 0x67, read 0x67, pass.

| |